本應用筆記主要介紹了將32.768K晶振連接到實時時鐘(RTC)的晶體選擇和布局技術.它還提供有關振蕩器電路設計標準,系統(tǒng)設計和制造問題的信息.

振蕩器基礎知識

振蕩器是皮爾斯型振蕩器的CMOS反相器變體.圖1顯示了一般配置.這些RTC包括集成負載電容(CL1和CL2)和偏置電阻.皮爾斯振蕩器利用以并聯(lián)諧振模式工作的晶體.并聯(lián)諧振模式中使用的晶體被指定為具有特定負載電容的特定頻率.為使振蕩器以正確的頻率運行,振蕩器電路必須使用正確的容性負載加載晶振.

圖1.帶內部負載電容和偏置電阻的RTC振蕩器.

準確性

基于晶體的石英晶體振蕩器電路的頻率精度主要取決于晶體的精度和晶體與振蕩器電容性負載之間匹配的精度.如果容性負載小于晶體設計的容量,則振蕩器運行速度很快.如果容性負載大于晶體設計的容量,則振蕩器運行緩慢.

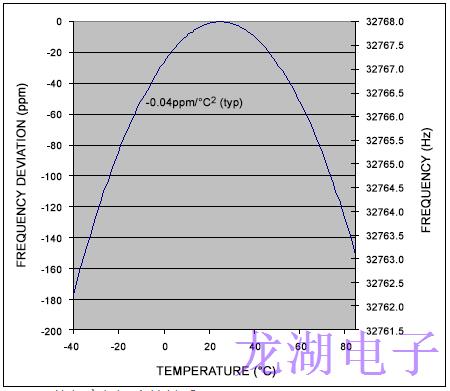

除了晶體和負載匹配的誤差之外,隨著環(huán)境溫度的變化,晶體的基頻也會發(fā)生變化.使用32.768K音叉晶體,它在溫度范圍內出現(xiàn)誤差,如圖2所示.誤差為20ppm相當于每月約1分鐘.

圖2.晶體頻率與溫度的關系.

注意:如果需要更高的精度,可以使用諸如DS32kHz的TCXO晶振.

水晶參數(shù)

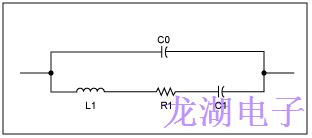

圖3顯示了晶體的等效電路.在諧振頻率附近,電路由包括運動電感L1,運動電阻R1和運動電容C1的串聯(lián)電路組成.并聯(lián)分量CO是晶體的并聯(lián)電容.

圖3.晶體等效電路.

負載電容CL是從石英晶振的引腳看到的振蕩電路的容性負載.圖4顯示了CL作為與晶體平行的電容.振蕩器電路中使用的負載電容CL1和CL2加上電路中的任何雜散電容組合在一起,形成總負載電容.所有均集成了CL1和CL2電容.應注意盡量減少印刷電路板(PCB)布局中的雜散電容.以下公式顯示了CL和負載電容值之間的關系:

CL=[(CL1×CL2)/(CL1+CL2)+CSTRAY]

圖4.晶體負載電容和等效并聯(lián)負載.

大多數(shù)晶體允許的最大驅動電平為1μW.所有RTC均低于1μW.可以使用以下公式確定驅動器級別:

P=2R1×[π×32,768(Cò+C大號)VRMS]²

其中VRMS是晶體兩端電壓的RMS值.

表1.晶體規(guī)格

| 參數(shù) | 符號 | 敏 | 典型 | 馬克斯 | 單位 |

| 標稱頻率 | f O. | 32.768 | 千赫 | ||

| 頻率容差 | delta f / f O. | ±20 | PPM | ||

| 負載電容 | C L | 6 | pF | ||

| 溫度轉換點 | T 0 | 20 | 25 | 30 | ℃ |

| 拋物線曲率常數(shù) | ? | 0.042 | PPM /℃ | ||

| 品質因素 | Q | 40000 | 70000 | ||

| 串聯(lián)電阻 | ESR | 45 | 千歐 | ||

| 分流電容 | C 0 | 1.1 | 1.8 | pF | |

| 電容比 | C 0 / C 1 | 430 | 600 | ||

| 駕駛級別 | D L | 1 | μW |

注1:某些器件允許更高的ESR值,請查看數(shù)據(jù)表以了解具體要求.

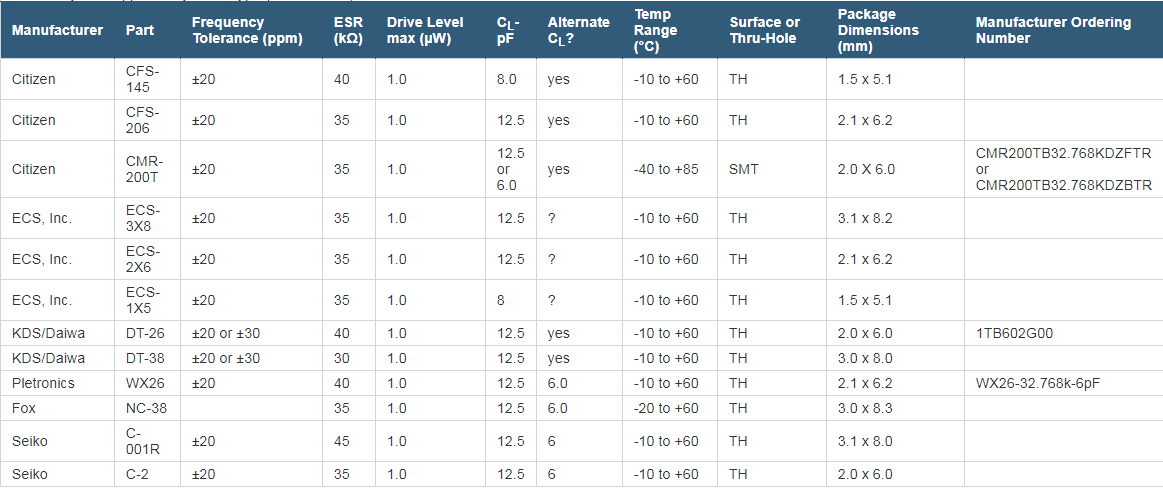

表2.晶體供應商,圓柱型(ESR=45kΩ)

注意:氣缸型尺寸為機筒直徑和長度,并排除導線.所有尺寸近似.

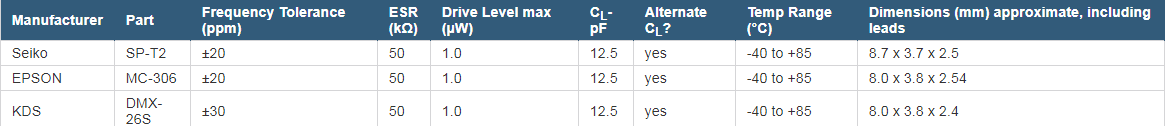

表3.晶體供應商,表面貼裝

振蕩器啟動時間

振蕩器啟動時間高度依賴于晶體特性,PCB泄漏和布局.高ESR和過大的容性負載是啟動時間長的主要原因.使用具有推薦特性和適當布局的32.768K晶振的電路通常在一秒鐘內開始.